|

[[stellae:wiki]]

|

Altera's ACEX generic dev. Board

This small board has been design to easily use ACEX 1K FPGAs from Altera in any project requiring a medium amount of logic. Only supplies and one clock are provided on board, leaving all user I/Os available on connectors. Power supply, JTAG & Passive Serial programming connector are also available.

ACEX 1K targets low-cost and low-density (from 576LEs to 4992LEs) applications. This device is fully supported by the free Quartus II Web Edition design tool. For more information on this FPGA, visit Altera's Web site.

This board is currently used in the low cost frame buffer/console for EFIKA project.

Schematics, GERBER & BOM

Schematics and Gerber files are available in PDF format. The BOM and Board pinout are Excel sheets.

Pictures

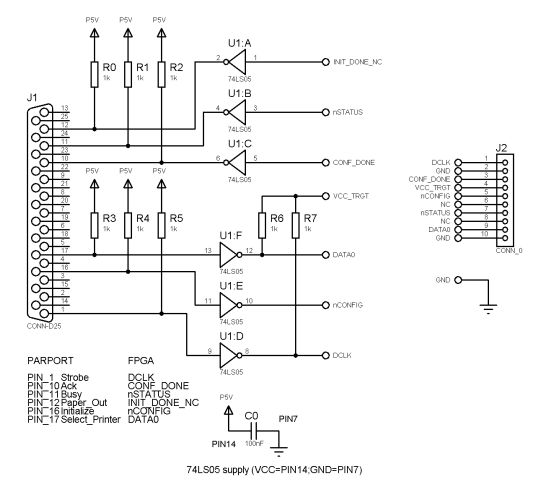

Passive serial programming

“Passive Serial” in one of the four configuration schemes available for ACEX FPGA. With this method, a microprocessor can download a configuration bitstream into the FPGA, removing the need for expensive download cables and/or dedicated external memories. For further information, you can read the CF51006 technical note from Altera.

You can find here a small PS (Passive Serial) interface I’ve designed to interface the ACEX board to any x86 PC equipped with a parallel port.

Schematics are available below.

This very simple interface only uses a 74HCT05 (or 74LS05). These open drain inverters make the 5V(parallel port)/3.3V(FPGA) voltage translation. DCLK and DATA0 requires pull-up resistors (tied to FPGA_VCC_IO 3.3V) because they are not available on the ACEX board.

|  |

You can find below various version of the software I have written to drive this I/F. The software is divided into several part in order to easily port the application to any embedded device. (Computer parport is just an example).

Source code, win32/Cygwin & static x86 build are available. In the Cygwin version see the readme.txt for installation instructions.

Some comments in the HAL_init() function (hal.c) are incorrect. For your convenience, you can download an up to date version.

This design is released under the terms of the GPL license. Many thanks to Cyril, the co-designer of this board.

Stellae (N. Lemouël) November, 2nd 2006 website@stellae.fr